## **IDDQ Data Analysis Using Current Signature**

James C.M. Li and Edward J. McCluskey CRC-Stanford University Stanford, CA 94305 cmli@crc.stanford.edu ejm@crc.stanford.edu

## **Abstract**

The goals of this paper are (1) to improve the effectiveness of IDDQ testing, and (2) to find the characteristic current signature for every defect class. Current signature analysis was performed for the IDDQ data collected on the Murphy test chip. A "total variance" method is proposed to reduce the test escape of IDDQ testing. Compared to the other three IDDQ testing methods, it has the lowest test escape and the highest yield loss. However, there are still 7.5% nonfunctional CUTs which could not be detected by any IDDQ testing method. This result shows that it is not possible to replace Boolean tests by IDDQ testing. The distributions of six current signature types over six different classes are analyzed. The results show that "big-step" is the dominant signature type among all defect classes.

### 1. Introduction

Past research has shown the importance of IDDQ testing in detecting defects that are not detected by Boolean tests, and hence improving quality levels [1,2]. Traditional single-threshold IDDQ testing in which a single current value is used to separate good and bad chips may be ineffective for chips with high background current and also lacks good diagnostic capability [3]. The concept of a current signature was recently introduced to improve IDDQ testing by carrying out a more precise analysis of IDDQ data [4,5]. This paper applies the current signature technique to analyze the IDDQ data collected on the Murphy test chip [6] to achieve the following two goals.

The first goal is to determine what the loss in test coverage would be if the only testing done was IDDQ testing with no Boolean tests. Research has shown that some chips that failed Boolean tests had low IDDQ and thus escaped the IDDQ tests [7]. To reduce test escapes when only IDDQ tests are applied, we propose an improved method for analyzing IDDQ current

signatures. By performing this analysis, we are trying to find out the possibility of detecting all the defective CUTs by doing only the IDDQ testing. This new method is compared with the other three existing methods, the single-threshold method, the current difference method and the vector-by-vector threshold method.

The second goal of this paper is to investigate the possibility of performing diagnosis by using current signature analysis. Research showed that IDDQ testing results may be useful in diagnosis [8,9,10]. But so far, there is no experimental data showing the relationship between current signatures and different defect classes. We analyzed the current signatures in every defect class to find out if there exists any characteristic signature which could be used for diagnosis.

The organization of this paper is as follows. Section 2 describes the Murphy test chip and the test vectors. Section 3 classifies the CUTs into six classes. Section 4 compares four IDDQ testing methods. Section 5 analyzes the current signatures for every defect class, and section 6 concludes the paper.

## 2. Test Chip and Test Set Description

The Murphy test chip uses the LSI Logic LFT150K FasTest array series. The nominal supply voltage is 5V and the effective channel length is 0.7µm. It is a 25K gate CMOS gate array. There are five kinds of CUTs on each die. Every kind of CUT has four copies. These dies were assembled in a 120pin ceramic pin grid array package and tested with the Advantest T6671E VLSI Test System. More details about this test chip can be found in [6]. The IDDQ test sets and test methods have been described in VTS-98 [11]. The resolution of the current measurements was 200nA. The wait time before each IDDO measurement was 1ms. Six IDDQ test sets were applied. They are generated or selected by different tools. Since the results from these six IDDQ tests are similar, we will only show the results from one test set for analysis.

Table 1 Population of each class

| Number of |         | Non-functional CUT |         |          | Functional CUT |          |  |

|-----------|---------|--------------------|---------|----------|----------------|----------|--|

| CUTs      | SSF TIC | Non-SSF TIC        | Non-TIC | VLV-only | IDDQ-only      | Pass-all |  |

|           | 38      | 29                 | 53      | 9        | 1              | 745      |  |

| Total     | 120     |                    |         |          | 755            |          |  |

### **Table 2 Distribution of maximum IDDQ**

| Boolean test | <1.5 µA | 1.5-3 μΑ | 3-5 μΑ | 5-10 μΑ | 10-20 μΑ | 20-50 μΑ | 50-100 μΑ | >100 µA | Total |

|--------------|---------|----------|--------|---------|----------|----------|-----------|---------|-------|

| Fail         | 2       | 17       | 3      | 1       | 2        | 4        | 4         | 87      | 120   |

| Pass         | 13      | 734      | 1      | 0       | 0        | 1*       | 4*        | 2*      | 755   |

<sup>\*</sup> outlier CUTs, not included in the calculation of standard signatures (see Section 4.2)

## 3. CUT Classification

We classified our CUTs into six classes according to their test results [12]. They are described as follows.

The behavior of a timing-independent-combinational (*TIC*) defect does not depend on the clock speed or the previous pattern. We generated a diagnostic dictionary for every possible single-stuck-at fault. We classified those TIC CUTs as *SSF TIC* if their values of the on-chip failure counters matched the numbers in the dictionary. For the other TIC CUTs that we could not find matches, we classified them as *non-SSF TIC*. A *non-TIC* CUT had either pattern dependent or timing dependent test results. The above three classes (SSF TIC, non-SSF TIC and non-TIC) failed at least one of the nominal voltage Boolean tests. They are called non-functional CUTs.

A CUT is classified as having a Very-Low-Voltage-only (*VLV-only*) failure if it passed all the Boolean tests at nominal voltage but failed some Boolean tests at very low voltage (in this experiment 2.5V and 1.7V) [13]. A CUT is classified as having *IDDQ-only* failure if it passed all the Boolean tests but its maximum IDDQ exceeded a certain limit (in this experiment, 3μA). A CUT is defined as *pass-all* if it passed all Boolean tests, VLV tests and single-threshold IDDQ tests. The above three classes (VLV-only, IDDQ-only and pass-all) are called functional CUTs.

The population distribution of each class is shown in Table 1. There are 120 non-functional CUTs and 755 functional CUTs totally. All CUTs from four wafer lots had similar IDDQ test results. Thus, we did the analysis on these four lots together.

# 4. Comparison of Four IDDQ Testing Methods

To improve the effectiveness of IDDQ testing, we propose a new method, the total variance

method. This method is compared with the other three existing methods. The details of these four methods are described below.

## 4.1 Single-threshold Method

This is the most commonly used IDDQ testing method. A current limit is chosen with care. Any CUT that has an IDDQ value larger than this threshold fails this test. The maximum IDDQ values measured in the Murphy experiment are shown in Table 2. Past research has shown that it is not easy to determine a current limit [7,11]. In this paper, we choose the limit to be 3 µA, one of the limit values used in [11].

Table 3 shows the results of this single-threshold IDDQ testing versus Boolean tests at nominal supply voltage. The first and the second columns show the 110 and 765 CUTs that failed and passed the singlethreshold IDDQ testing respectively. The first row shows the 120 non-functional CUTs. 102 of them failed the single-threshold IDDQ test but 18 passed. The test escape percentage of this IDDQ testing method is therefore 15% (18/120). The second row shows the 755 functional CUTs. 747 of them passed the single-threshold IDDQ testing but eight failed. The yield loss percentage of this IDDQ testing method is therefore 1.1% (8/755). (In this paper, the test escape percentage is defined as the fraction of non-functional CUTs that passed the IDDQ testing. The yield loss percentage is defined as the fraction of functional CUTs that failed the IDDQ testing. Please read Section 4.5 for more detailed discussions.)

**Table 3 Single-threshold method**

|                  | Fail single-threshold (110)                | Pass single-threshold (765)                |

|------------------|--------------------------------------------|--------------------------------------------|

| Non-func. (120)  | 102<br>30/25/47<br>SSF/non-SSF TIC/non-TIC | 18<br>8/4/6<br>SSF/non-SSF TIC/non-TIC     |

| Functional (755) | <b>8</b><br>7/1/0<br>VLV/IDDQ/pass-all     | <b>747</b><br>2/0/745<br>VLV/IDDQ/pass-all |

#### **4.2 Current Difference Method**

As the number of transistors on a die gets larger and the threshold voltage gets lower, the background current increases. This makes it difficult to choose a single-threshold value for IDDQ testing [3,14]. In this experiment, we took the absolute difference between the first IDDQ (which is usually one of the largest IDDQ because the first vector usually has the highest coverage) and the other IDDQ measurements in order to take away the background current. A CUT failed this test if the current difference was greater than a certain limit. In this experiment, we also set the limit to be 3  $\mu A$ .

The results are shown in Table 4. Compared to the single-threshold method, this method gave two more test escapes than the single-threshold method. These two CUTs belong to the non-TIC class. They had constant current signatures (see Section 5). For the functional CUTs, this method had the same results as the single-threshold method.

Fail current difference (108) Pass current difference (767) Non-func. (120) 20 100 30/25/45 8/4/8 SSF/non-SSF TIC/non-TIC SSF/non-SSF TIC/non-TIC Functiona 8 747 2/0/745 7/1/0VLV/IDDQ/pass-all VLV/IDDQ/pass-all

**Table 4 Current difference method**

## 4.3 Vector-by-vector Threshold Method

Although the single-threshold method is used in industry, researchers have shown that it is not easy to determine one single threshold value [7,11]. Some researchers suggested that the threshold value should be different for each IDDQ test vector [15]. We followed the same flow as in [15] to perform data analysis:

- (1)From the 755 functional CUTs, we removed 7 CUTs with maximum IDDQ 10 times higher than the IDDQ value which the major population had (CUTs with stars in Table 2). They called these CUTs "outliers" in [15]. By removing these outlier IDDQ data, a further statistical analysis could be performed on the remaining CUTs.

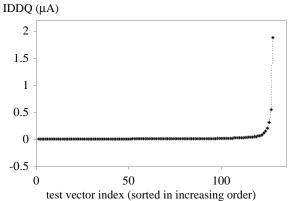

- (2)For each IDDQ test vector, we calculated the mean and standard deviation (σ) from the remaining 748 CUTs. The means are sorted in increasing order. We call this curve the *standard signature*. One example standard signature is given in Fig. 1. If a CUT has any one IDDQ measurement that exceeds the standard signature

by a certain limit, the CUT fails this test. In this paper, the limit was set to be four  $\sigma$ .

Figure 1 A standard signature (thick dots)

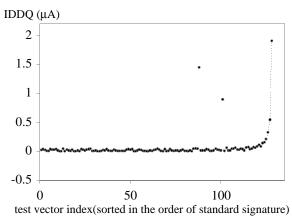

An example is shown in Fig. 2. This CUT belongs to the SSF TIC class. The thin dotted line is the standard signature. The thick dots are the IDDQ of the CUT being analyzed (sorted in the same order as the standard signature). This CUT had a maximum IDDQ value less than  $3\,\mu A$  and very different IDDQ measurements from the standard signature. It would pass the  $3\mu A$  single-threshold method but fail the vector-by-vector threshold method.

Figure 2 IDDQ of a SSF CUT (thick) versus standard signature (thin)

The results of this method are shown in Table 5. Compared to the single-threshold method, it detected six more non-functional CUTs than the single-threshold method. The test escape percentage was improved by 5% (6/120). However, this method failed one more functional CUT than the single-threshold method. The yield loss percentage was worsened by 0.1% (1/755).

Table 5 Vector-by-vector threshold method

|                    | Fail vector-by-vector (117)                | Pass vector-by-vector (758)                |

|--------------------|--------------------------------------------|--------------------------------------------|

| Non-func. (120)    | 108<br>34/25/49<br>SSF/non-SSF TIC/non-TIC | 12<br>4/4/4<br>SSF/non-SSF TIC/non-TIC     |

| Functiona<br>(755) | <b>9</b><br>8/1/0<br>VLV/IDDQ/pass-all     | <b>746</b><br>1/0/745<br>VLV/IDDQ/pass-all |

### **4.4 Total Variance Method**

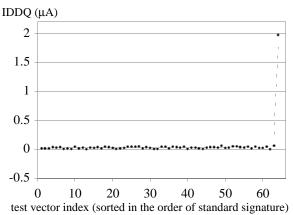

According to our observations, there were still some non-functional CUTs that did not exceed the four  $\sigma$  vector-by-vector threshold. In Fig. 3, a CUT with a single-stuck-at fault is shown as an example. The thin dotted line is the standard signature and the thick dots are the IDDQ of the CUT being analyzed (sorted in the same order of the standard signature). Every single IDDQ measurement does not deviate from the standard signature by four  $\sigma$  yet the whole curve looks different from the standard signature. Based on this observation, we therefore propose a total variance method:

Figure 3 IDDQ of a SSF CUT (thick) versus standard signature (thin)

- (1)We summed up all the variances (error square) of an IDDQ curve with respect to the standard signature for all the vectors. We call this the *total variance*. This number represents how different the IDDQ curve being analyzed is from the standard signature. This total variance was used as an indicator to decide whether a CUT passes or fails the test.

- (2)The distribution of the total variance of the 748 CUTs (see Section 4.3) is shown in Table 6-1. As was done in Section 4.3, we removed 2 outlier CUTs with total variances ten times higher than the total variance of the major population. The

means and  $\sigma$  of the total variances were then generated for the remaining 746 CUTs. See Table 6-2.

(3)If the total variance of a CUT exceeded the mean in Table 6-2 by four  $\sigma$ , it failed the test.

Table 6-1 Distribution of the total variance unit:  $\mu A^2$  (5 kinds of CUTs)

|     |       | •     | •    |        | ,    |       |

|-----|-------|-------|------|--------|------|-------|

| CUT | < 0.1 | 0.1-1 | 1-10 | 10-100 | >100 | total |

| Sqr | 149   | 1     | 0    | 1*     | 0    | 151   |

| Mul | 148   | 1     | 0    | 0      | 0    | 149   |

| Rob | 148   | 1     | 0    | 0      | 0    | 149   |

| Elm | 1     | 135   | 13   | 0      | 1*   | 150   |

| Std | 148   | 1     | 0    | 0      | 0    | 149   |

\* outlier CUTs, not included in the calculation of Table 6-2.

Table 6-2 Mean and  $\sigma$  of the total variance (5 kinds of CUTs)

| CUT | Mean (unit: μA <sup>2</sup> ) | $\sigma$ (unit: $\mu A^2$ ) |

|-----|-------------------------------|-----------------------------|

| Sqr | 0.017                         | 0.021                       |

| Mul | 0.019                         | 0.024                       |

| Rob | 0.035                         | 0.041                       |

| Elm | 0.400                         | 0.800                       |

| Std | 0.019                         | 0.024                       |

The results are shown in Table 7. Compared to the vector-by-vector threshold method, this method detected three more non-functional CUTs than the vector-by-vector threshold method. The test escape percentage was improved by 2.5% (3/120). But this method failed 13 more functional CUTs than the vector-by-vector method. The yield loss percentage was worsened by 1.1% (13/755).

**Table 7 Total variance method**

|                  | Fail total variance (133)                  | Pass total variance (742)                  |

|------------------|--------------------------------------------|--------------------------------------------|

| Non-func. (120)  | 111<br>35/25/51<br>SSF/non-SSF TIC/non-TIC | 9<br>3/4/2<br>SSF/non-SSF TIC/non-TIC      |

| Functional (755) | 8/1/13<br>VLV/IDDQ/pass-all                | <b>733</b><br>1/0/732<br>VLV/IDDQ/pass-all |

### 4.5 Comparison and discussion

Table 8 shows the pass/fail distribution of the 120 non-functional CUTs. One hundred of them failed all four methods, but nine of them passed all. These nine CUTs can not be distinguished from the functional CUTs by performing only the IDDQ testing. This result shows that Boolean tests can not be replaced by the IDDQ testing.

### Table 8 Pass/fail distribution

120 non-functional CUTs (SSF/non-SSF TIC/non-TIC)

Vector-by-vector threshold

|          |     | F        | P     | F     | P     |     |         |

|----------|-----|----------|-------|-------|-------|-----|---------|

|          | F   | 100      | 0     | 0     | 0     | F   |         |

| -        | .1] | 30/25/45 | 0/0/0 | 0/0/0 | 0/0/0 | . 1 | Cur     |

| Total    | F   | 2        | 0     | 6     | 3     | P   | rent    |

|          |     | 0/0/2    | 0/0/0 | 4/0/2 | 1/0/2 |     | _       |

| variance | P   | 0        | 0     | 0     | 0     | F   | differe |

| anc      |     | 0/0/0    | 0/0/0 | 0/0/0 | 0/0/0 | . 1 | ere     |

| ë        | P   | 0        | 0     | 0     | 9     | P   | nce     |

|          |     | 0/0/0    | 0/0/0 | 0/0/0 | 3/4/2 |     | æ       |

|          |     | F        | F     | P     | P     |     |         |

Single-threshold

Two non-TIC CUT passed the current difference method because they had constant IDDQ. Six non-functional CUTs were detected by both the vector-by-vector threshold and the total variance method. Three non-functional CUTs were detected only by the total variance method.

Table 9 shows the pass/fail distribution of the 755 functional CUTs. 733 of them passed all four methods but eight of them failed all. One VLV-only CUT failed both the vector-by-vector threshold method and the total variance method. Thirteen pass-all CUTs failed the total variance method. A total of 22 functional CUTs failed at least one of the four IDDQ testing methods.

Table 9 Pass/fail distribution

755 functional CUTs (VLV-only/IDDQ-only/pass-all)

Vector-by-vector threshold

|          |    |       | •     |       |         |     |            |

|----------|----|-------|-------|-------|---------|-----|------------|

|          |    | F     | P     | F     | P       | ]   |            |

|          | H  | 8     | 0     | 0     | 0       | F   |            |

| -        | į, | 7/1/0 | 0/0/0 | 0/0/0 | 0/0/0   | . 1 | Ħ          |

| Total    | Ŧ  | 0     | 0     | 1     | 13      | P   | rent.      |

|          |    | 0/0/0 | 0/0/0 | 1/0/0 | 0/0/13  |     |            |

| variance | d  | 0     | 0     | 0     | 0       | F   | difference |

| anc      |    | 0/0/0 | 0/0/0 | 0/0/0 | 0/0/0   | - 1 | ere        |

| ĕ        | d  | 0     | 0     | 0     | 733     | P   | nce        |

|          |    | 0/0/0 | 0/0/0 | 0/0/0 | 1/0/732 |     | ()         |

|          |    | F     | F     | P     | P       |     | _          |

${\bf Single-threshold}$

In this paper, the yield loss is defined as the fraction of functional CUTs that passed the Boolean

tests at nominal voltage but failed the IDDQ testing. Whether or not these CUTs are really reliable is not known yet. These CUTs may be defective even if they passed the Boolean tests at the nominal supply voltage. We plan to burn-in these 22 functional CUTs (see Table 9) to see if they have early-life failure.

Table 10 summarizes the test escape and the yield loss of these four methods. The total variance method has the best performance in the test escape and the worst in the yield loss. The current difference method performs the worst in the test escape.

Table 10 Summary of test escape, yield loss

|                    | Test escape | Yield loss |

|--------------------|-------------|------------|

| Method             | (120 CUTs)  | (755 CUTs) |

| Single-threshold   | 18 (15%)    | 8 (1.1%)   |

| Current difference | 20 (16.7%)  | 8 (1.1%)   |

| Vector-by-vector   | 12 (10%)    | 9 (1.2%)   |

| Total variance     | 9 (7.5%)    | 22 (2.9%)  |

Although the total variance method has the least test escapes, the longer testing time and higher testing cost required should be taken into account to have a fair comparison. Using the single-threshold IDDQ testing method, a bad chip can be discarded as soon as any single IDDQ measurement exceeds the current limit. Using the current difference method, a bad chip can be discarded as soon as any current difference value exceeds the limit. However, using the total variance and the vector-by-vector threshold methods, all the IDDQ data has to be recorded and then post-processed. Furthermore, the total variance method requires higher accuracy in IDDQ measurement so that it may only be performed in the package test, not in the wafer probe.

There are two more comments about the 745 pass-all CUTs. First, only 309 (out of 5,491) dies were selected and packaged. Hence, the 745 pass-all CUTs were just a small portion of a large population of good CUTs. Secondly, in the Murphy experiment, we applied many more Boolean test vectors than is customary. Therefore, the current signatures of these pass-all CUTs might be very similar to each other.

Table 11 Current signature type distribution in each class

| Table 11 can old |             |                    |             |            |                |              |  |

|------------------------------------------------------|-------------|--------------------|-------------|------------|----------------|--------------|--|

| current signature                                    |             | Non-functional CUT | 7           |            | Functional CUT |              |  |

| type                                                 | SSF TIC     | Non-SSF TIC        | Non-TIC     | VLV-only   | IDDQ-only      | pass-all     |  |

| big-step                                             | 23 (60.5%)  | 21 (72.4%)         | 30 (56.6%)  | 2 (22.2%)  | 0 (0.0%)       | 0 (0.0%)     |  |

| small-step                                           | 2 (5.3%)    | 0 (0.0%)           | 5 (9.4%)    | 5 (55.6%)  | 1 (100.0%)     | 0 (0.0%)     |  |

| increasing                                           | 2 (5.3%)    | 2 (6.9%)           | 4 (7.5%)    | 0 (0.0%)   | 0 (0.0%)       | 0 (0.0%)     |  |

| constant                                             | 0 (0.0%)    | 0 (0.0%)           | 2 (3.8%)    | 0 (0.0%)   | 0 (0.0%)       | 0 (0.0%)     |  |

| small                                                | 8 (21.1%)   | 4 (13.8%)          | 6 (11.3%)   | 2 (22.2%)  | 0 (0.0%)       | 745 (100.0%) |  |

| others                                               | 3 (7.9%)    | 2 (6.9%)           | 6 (11.3%)   | 0 (0.0%)   | 0 (0.0%)       | 0 (0.0%)     |  |

| total                                                | 38 (100.0%) | 29 (100.0%)        | 53 (100.0%) | 9 (100.0%) | 1 (100.0%)     | 745 (100.0%) |  |

## 5. Current Signature Analysis

We analyzed the current signatures in every class. We classified the current signatures into six types:

- (1)big-step: current signatures with one or more abrupt steps (discontinuity in signatures) greater than  $100 \, \mu A$ .

- (2)small-step: current signatures with one or more small abrupt steps ( $< 100 \, \mu A$ ).

- (3)increasing: current signatures which increase gradually without abrupt steps and have maximum IDDQ greater than 10 μA.

- (4)constant: current signatures with constant IDDQ for every test vector (pattern independent) and maximum IDDQ  $> 10 \mu A$ .

- (5)small: current signatures with very low maximum IDDQ (<  $10 \,\mu A$ ).

- (6)others: current signatures that do not belong to any of the above types.

The distribution of these six current signature types in each class is shown in Table 11. Our observations are as follows:

- (1)Big-step is the dominant signature type among all non-functional CUTs.

- (2)The VLV-only CUTs had more small-step current signatures than the other classes. The reason might be that VLV tests detect some high-resistive shorts better than nominal voltage tests do. These CUTs with small-step current signatures have maximum IDDQ less than 100 μA. These CUTs may pass a single-threshold IDDQ test with a high current limit. However, some of these CUTs may have high-resistive shorts which may cause problems in the future.

- (3)Two CUTs in the non-TIC class had constant current (50μ A and 18μ A respectively). One possible explanation might be that they have pattern independent defects which caused delay faults (like a short between the input and output of an inverter). These two CUTs showed that small but constant IDDQ might be harmful.

- (4)In our data, we did not find any CUT that passed all Boolean tests but had constant DC current. On the other hand, constant current signature was only seen in the non-TIC class.

### 6. Conclusions

In this paper, we propose a total variance method to analyze the IDDQ data collected on the Murphy test chip. Compared to the other three methods, it has the lowest test escape. But there are still 9 out of the 120

non-functional CUTs (7.5%) which had identical current signatures as the pass-all CUTs. These 7.5% CUTs can not be distinguished from the functional CUTs by performing only the IDDQ testing. This result shows that Boolean tests can not be replaced by the IDDQ testing.

We also show the current signature distributions of the six different classes. We find out that many VLV-only CUTs have the feature of small-step current signatures. For the other defect classes, big-step is the most common signature. But so far, we have not found any signature type that belongs to one particular defect class.

## Acknowledgements

The authors would like to thank Jonathan Chang, Chao-Wen Tseng, Siegrid Munda,, Nirmal Saxena, Nancy Shen and Ying-Chih Chuang for their precious comments.

#### References

- [1] P. Maxwell, et.al., "The Effectiveness of IDDQ, Functional and Scan Tests: How many fault coverage do we need?" *Proc. International Test Conference*, pp. 168-177, Dec. 1992.

- [2] Rodriguez-Montanes, et.al., "Current vs. logic Testing of Gate Oxide short, Floating Gate and Bridging Failures in CMOS," *Proc. International Test Conference*, pp. 510-518, Oct. 1991.

- [3] J.M. Soden and C.F. Hawkins, "IDDQ Testing: Issues Present and Future", *IEEE Design and Test of Computers*, pp. 61-65, Winter 1996.

- [4] A.E. Gattiker and W. Maly, "Current Signatures," *Proc. IEEE VLSI Test Symposium*, pp. 112-117, April 1996.

- [5] A.E. Gattiker and W. Maly, "Current Signatures: Application," Proc. International Test Conference, pp. 156-165, Nov. 1997.

- [6] P. Franco, et.al., "An Experimental Chip to Evaluate Test techniques Chip and Experiment Design," Proc. International Test Conference, pp. 653-662, Oct. 1995.

- [7] P. Nigh, et.al., "So What Is An Optimal Test Mix? A Discussion of the SEMATECH Methods Experiment," Proc. International Test Conference, pp. 1037-1038, Nov. 1997

- [8] P. Nigh, et.al., "An Experiment Study Comparing the Relative Effectiveness of Functional, Scan, IDDQ and Delay-fault Testing," *IEEE VLSI Test Symposium*, pp. 459-464, April 1997.

- [9] P. Nigh, ét.al., "Failure Analysis of Timing and IDDQonly Failure from the SEMATECH Test Methods Experiment," Proc. International Test Conference, 1998.

- [10] C. Henderson and J. Soden, "Signature Analysis for IC Diagnosis and Failure Analysis," Proc. International Test Conference, pp. 310-318, Nov. 1997.

- [11] J.T.-Y. Chang et.al., "Experimental Result for IDDQ and VLV Testing," *Proc. IEEE VLSI Test Symposium*, pp. 118-123, April 1998.

- [12] P. Franco, et.al., "Analysis and Detection of Timing Failures in an Experimental Test Chip," *Proc. International Test Conference*, pp. 691-700, Oct. 1996.

- [13] J.T.-Y. Chang et.al., "Quantitative Analysis of Very Low-Voltage Testing," Proc. IEEE VLSI Test Symposium, pp. 332-337, April 1996.

- [14] S. Davidson, "Is IDDQ yield Loss Inevitable?," Proc. International Test Conference, pp. 572-578, 1994.

- [15] T.R.Henry and T.Soo, "Burn-in Elimination of a High Volume Microprocessor Using IDDQ," Proc. International Test Conference, pp. 242-249, Oct. 1996.